Назад

Схема высокоскоростного мягкого старта, встраиваемая в DC/DC-преобразователь

Авторы статьи

Полезные ссылки

(Опубликовано в журнале «Вестник Электроники», №2 2014)

Скачать статью в формате PDF (384 КБ)

В статье представлена полностью встроенная в понижающий DC/DC-преобразователь схема мягкого старта. Обладающая малым временным интервалом, она состоит из двух секций: схема подавления перерегулирования и схема подавления выбросов тока при включении. Схема подавления перерегулирования создана для управления по входу усилителя ошибки, чтобы задать пошаговый рост ограничения выходного напряжения без использования внешнего конденсатора. В схеме подавления выбросов тока применяется тактовый сигнал с изменяющейся часто-той для повышения скважности тактирования всей системы. DC/DC-преобразователь с предложенной схемой мягкого старта был изготовлен с использованием стандартной 0,13-мкм CMOS-технологии. Практические результаты показали, что данный преобразователь дает время мягкого старта в 50 мкс. Ток индуктивности и выходное напряжение растут плавно во всем диапазоне нагрузок.

Введение

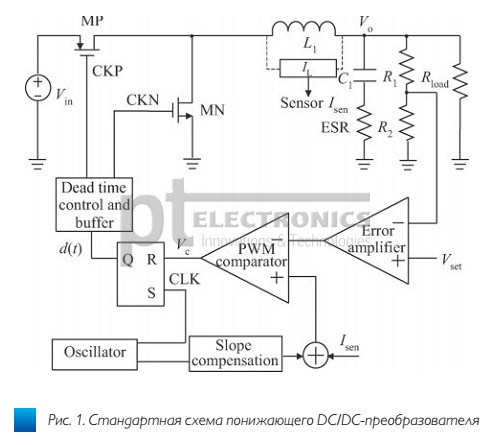

В последнее время импульсные источники питания широко применяются в портативных электронных системах (устройствах) благодаря их высокой производительности, стабильности и динамическим характеристикам. Стандартная блок-схема понижающего DC/DC-преобразователя, управляемого током, представлена на рис. 1.

Корректирующая цепь преобразует сигнал ошибки в изменение скважности сигнала, который управляет переключающим элементом. Проблема заключается в том, что в начале запуска преобразователя переходная характеристика усилителя ошибки неустойчива, а это заставляет преобразователь работать на импульсах 100%-ной скважности. Данная ситуация вызывает рост тока на катушке индуктивности выше номинального значения и, как следствие, появление выбросов тока. Данное повышенное значение тока будет сохраняться в течение небольшого временного интервала, так как ток катушки не может измениться моментально. В результате может возникнуть резкий скачок выходного напряжения, превышающий свое стандартное значение. Электронная система может быть повреждена во время запуска всплеском тока и напряжения. Для ликвидации данного явления требуется цепь мягкого старта.

Наиболее стандартный метод задания плавного роста выходного напряжения — использование внешнего конденсатора Сsoft. Выход усилителя ошибки или опорное напряжение Vset растут постепенно, когда Сsoft заряжен линейно. Время мягкого старта преобразователя зависит от емкости Сsoft и тока его зарядки. Этот метод имеет простой принцип и может быть легко реализован, однако используемый конденсатор обычно обладает слишком большими габаритами для установки на плату. Другой метод ограничения выходного напряжения основан на тактируемой цепи мягкого старта, которая может точно контролировать время запуска. Оба эти метода разработаны для контроля напряжения на выходе преобразователя. Вдобавок, метод снижения всплесков тока определяет ток индуктивности и сравнивает его значение c установившимся значением постоянного тока на выходе преобразователя. Учитывая, что значение ограничиваемого тока обычно выше максимального рабочего, то в фазе мягкого старта используется кусочно-ограниченный (или порционально-ограниченный) ток. Однако в оценке изменения выходных параметров используется компаратор, поэтому данный метод не подходит для преобразователей, которые не имеют функции ограничения выходного тока.

В данной статье предлагается схема с простым цифроаналоговым преобразователем и изменяющейся минимальной скважностью импульсов для подавления всплесков напряжения и тока на выходе преобразователей с варьируемым выходным напряжением.

Схема мягкого старта

Представленная схема мягкого старта основана на принципе традиционного управляемого током преобразователя. Схема состоит из двух частей: подавления повышенного напряжения и подавления всплеска тока.

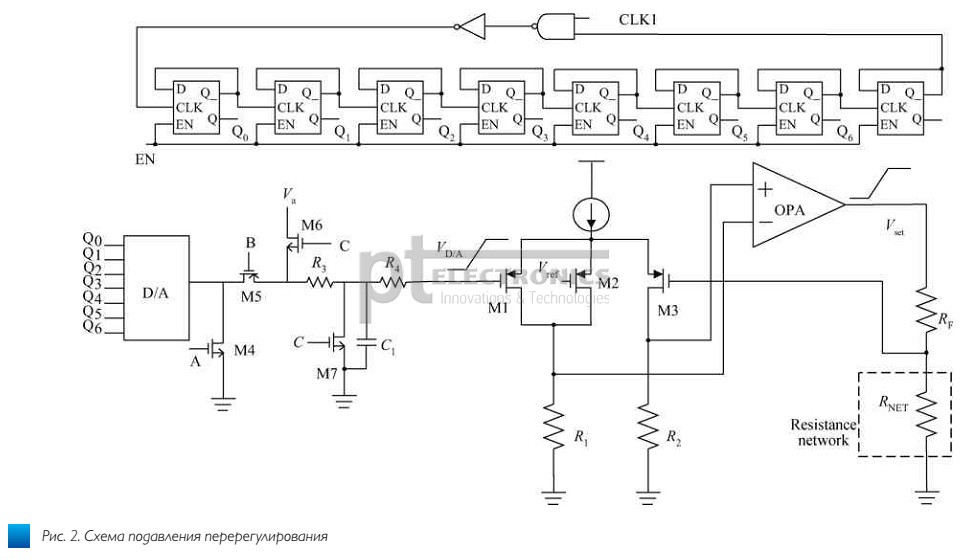

В начале запуска напряжение Vset значительно превышает Vo, что делает усилитель ошибки неустойчивым. В таком случае он может повредить всю систему. Очевидно, что плавное повышение напряжения может формироваться сложением Vset со ступенчатым напряжением, что показано на рис. 2. Ступенчатое напряжение генерируется с помощью цифро-аналогового преобразователя (D/A). Более того, из-за минимальной скважности, используемой в преобразователе, всплески тока будут генерироваться в первоначальной стадии. В данной статье предлагается варьируемая минимальная скважность для подавления всплесков тока.

Цепь защиты от перенапряжения

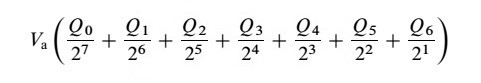

Как показано на рис. 2, разработанная схема подавления всплесков напряжения реализована внутренней цепью, которая обычно содержит три секции: ЦАП, цепь сопротивлений, и OPA (Optical Parameter Amplifier, операционный усилитель). OPA и цепь сопротивлений служат для задания соответствия варьируемого несущего напряжения с динамическим напряжением, являющимся характеристикой DC/DC-преобразователя. Выход ЦАП может быть представлен как:

Напряжение на выходе ЦАП растет постепенно, пока таймер считает цифровой сигнал от 7b‘0000000 до 7b‘1000000’. Когда сигнал отсчитывается от 7b‘0000000 до 7b‘1000000’, MOS-транзисторы М4 и М5 выключены, в то время как М6 и М7 включены для предотвращения уменьшения выходного напряжения ЦАП. Таким образом, на выходе ЦАП будет оставаться напряжение Vа. Данная структура делает возможным рост напряжения с ЦАП до стабильного установившегося значения.

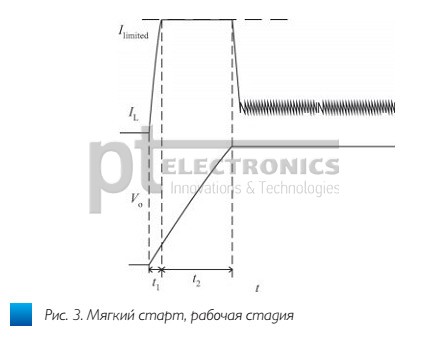

Время мягкого старта определяется счетчиком, который контролирует ЦАП. Наименьшим оно будет в том случае, когда система использует сигнал максимальной скважности для ограничения тока. В свою очередь мягкий старт состоит из двух фаз. Если всплеска тока нет, то система будет работать, используя максимальную скважность до ограничения тока Ilimited, а затем работать, используя Ilimited до тех пор, пока напряжение не достигнет установившегося значения. Рабочая стадия показана на рис. 3.

Таким образом, наиболее короткий период времени может быть посчитан при использовании следующих двух правил:

- Система работает на максимальной скважности до ограниченного тока.

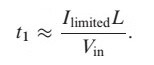

t1— это время, когда система работает, используя максимальную скважность до ограниченного тока, как показано на рис. 3. Поскольку приращение выходного напряжения очень мало, то оно принимается равным нулю. В таком случае время t1 может быть описано следующим выражением:

- Система работает, используя ограниченный ток до тех пор, пока выходное напряжение не станет стабильным.

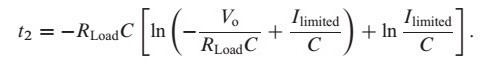

Как показано на рис. 3, t2 — время, когда система работает используя ограниченный ток до тех пор, пока выходное напряжение не достигнет установившегося значения. Ток катушки индуктивности остается постоянным. Таким образом, процесс зарядки может быть выражен следующим образом:

Время t2 может быть посчитано, исходя из дифференциальных уравнений:

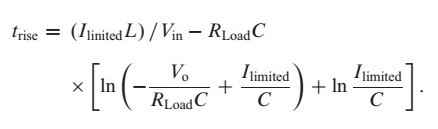

Следовательно, наименьшее время является суммой двух частей:

Очевидно, что в случае большей нагрузки требуется большее время, чем при малой нагрузке. В представленной схеме время роста Vset сделано специально большим, чем trise , чтобы добиться сбалансированного подавления превышающего значения Vo и достижения мягкого старта.

Как указывалось выше, семибитный ЦАП будет задавать медленный рост напряжения на затворе транзистора М1 (рис. 2). Тем не менее, напряжение на затворе транзистора М2, которое больше, чем напряжение на затворе М1, зафиксировано на значении Vset, так что в начальной фазе мягкого старта транзистор М2 выключен. А ток затвора М1, М2 и М2 будет всегда соответствовать:

Из-за виртуального КЗ между входами операционного усилителя напряжение на затворе транзистора М3 будет расти с ростом на транзисторе М1. Более того, в данной фазе IМ1 будет уменьшаться во время роста IM2 для сохранения баланса тока. Когда напряжение на затворе транзистора М1 достигнет определенного значения, транзистор М1 отключится. В этот момент IМ2= IМ3. Мягкий старт и формирование выходного напряжения завершится успешно. Поэтому Vo будет увеличиваться до задающего напряжения Vset. В свою очередь Vset задается цепью сопротивлений.

Цепь подавления всплесков тока

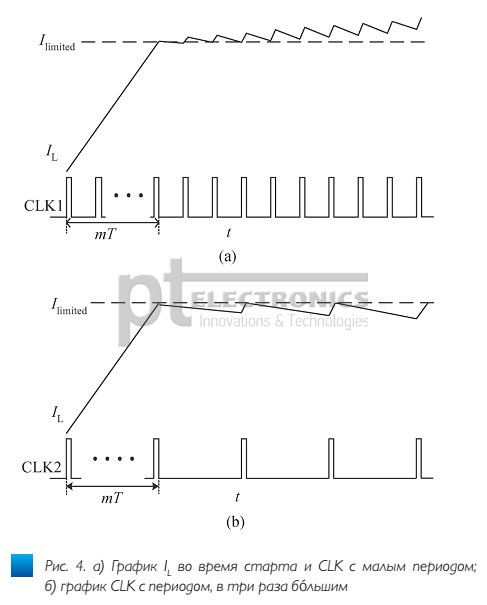

С целью предотвращения полного закрытия силового MOSFET, а также с целью подавления шумов, влияющих на стабильность преобразователя между открытием и закрытием MOSFET, в нашем DC/DC-преобразователе используется тактирующий генератор (CLK), обеспечивающий минимальную скважность. Во время мягкого старта из-за того, что выходное напряжение слишком мало, преобразователь будет работать на импульсах максимальной скважности. В течение m циклов ток индуктивности растет до порогового значения, как показано на рис. 4.

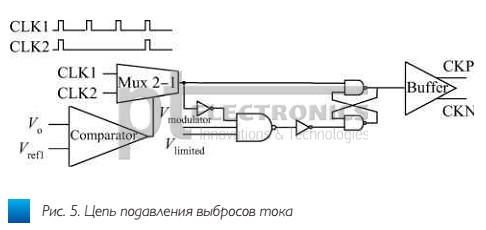

Когда сигнал CLK имеет высокий уровень, выход модулятора и сигнал ограничения тока заблокированы, как показано на рис. 5

С другой стороны, при низком уровне работают модулятор и цепь ограничения тока. Затем ток катушки будет уменьшаться — из-за того, что работает цепь ограничения тока. А когда сигнал тактового генератора имеет высокий уровень, ток катушки будет все еще увеличиваться, как показано на рис. 4. Наклон кривой роста тока катушки: Kup_slope = (Vin–Vo)/L, наклон спада тока: Kdown_slope= Vo/L. Очевидно, что наклонная линия заряда значительно круче, чем наклонная линия разряда в начальной стадии роста Vo. Как показано на рис. 4а, ток индуктивности превысит лимит тока после нескольких циклов; затем генерируется всплеск тока. Основная причина генерирования всплеска тока заключается в том, что ток зарядки гораздо выше тока разрядки. Учитывая проблемы, указанные выше, в предложенной схеме мягкого старта применяется тактирование импульсами с частотой, уменьшенной втрое.

Как показано на рис. 5, в начальной фазе, т. е. когда Vo меньше Vref1, применяются тактовые импульсы малой скважности, формируемые тактовым генератором CLK2, и тогда ток разряда будет больше, чем во время работы генератора CLK1. Затем, когда Vo становится больше Vref1, система переключается на генератор CLK1. Как показано на рис. 4б, три такта (clock cycles) CLK1 содержатся в такте CLK2. В начальной фазе время, которое система тратит на рост тока до ограниченного значения, одно и то же. Когда время разряда индуктивности дольше, а время заряда меньше, преобразователь работает на тактовом генераторе CLK2. Очевидно, что ток индуктивности будет нарастать медленнее и убывать быстрее, когда преобразователь работает на CLK2. Ток заряда меньше, чем тока разряда, следовательно, всплеск тока при запуске преобразователя может быть легко подавлен. В случае, когда напряжение Vo больше Vref1, система автоматически переключается на тактовый генератор CLK1. Задача этой цепи — установить напряжение Vref1. Данное напряжение устанавливается согласно следующим правилам:

- Когда схема переключается на CLK1, ток зарядки должен быть равен или меньше тока разряда. В противном случае схема будет генерировать повышенные импульсы тока после переключения на CLK1, и цепь подавления всплеска тока потеряет свою функцию.

- Ток индуктивности должен быть меньше ограниченного тока, когда схема переключается на CLK1. Это будет гарантировать, что цепь не генерирует выброс тока.

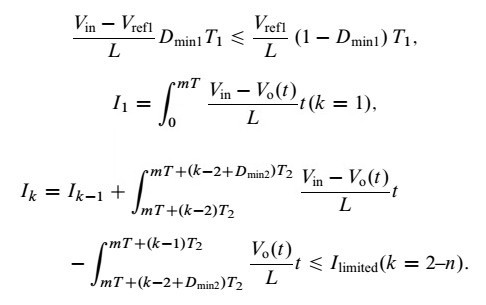

Оба эти пункта могут быть описаны следующими формулами:

Здесь Dmin1— это минимальная скважность, когда конвертер работает от CLK1, а Dmin2— минимальная скважность при работе генератора CLK2; T1 — период CLK1, T2 — период CLK2. Периоды T1 и T2 имеют следующее соотношение: 3T = 3T1 = T2. Постоянные значения используются для замены изменяющегося напряжения Vo. Когда I≤I1, Vo(t)≈0. Когда I2≤I≤In/3, Vo(t)≈1/3Vref1. При In/3≤I≤I2n/3 Vo≈2/3Vref1. Если I2n/3≤I≤In, Vo(t)≈Vref1.

В случае, когда Vo больше, чем Vref1, система автоматически переключается на CLK1. В это время ток заряда эквивалентен току разряда, пока выходное напряжение растет до заданного значения. При наступлении стабильности ток будет уменьшаться, и фаза запуска будет завершена.

Моделирование и результаты измерений

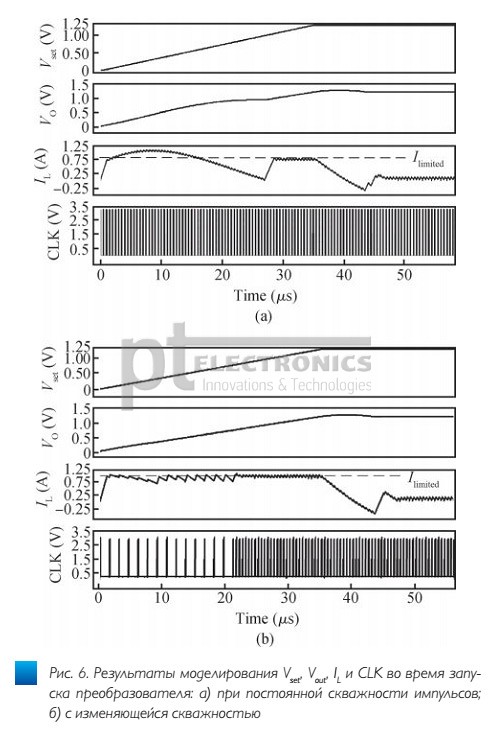

Предложенная схема выполнена на 13-мкм CMOS-технологии китайской фирмы по производству электроники SMIC. Сравнительные результаты моделирования показаны на рис. 6. Графики, приведенные на рис. 6а, — это результат моделирования при работе на импульсах малой скважности. Очевидно, что при этом всплески тока все еще имеются. Ток индуктивности будет превышать свое номинальное значение даже спустя несколько циклов. Но на рис. 6б мы видим изменение скважности импульсов и убеждаемся в том, что выбросы тока эффективно контролируются. Результаты моделирования соответствуют теоретическому анализу.

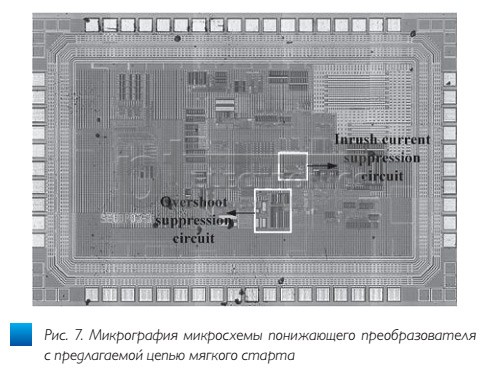

DC/DC-преобразователь со схемой мягкого старта был выполнен на 0,13-мкм технологии CMOS SMIC. Микрография преобразователя представлена на рис. 7. Площадь предложенной в данной статье схемы составляет лишь 0,006 мм2. Входное напряжение преобразователя равно 3,3 В, а выходное — 1,5 В.

В статье описана встроенная цепь мягкого старта, состоящая из цепи подавления перерегулирования и цепи подавления выбросов тока. Цепь подавления перерегулирования генерирует плавно возрастающее напряжение, которое может эффективно подавлять превышения выходного напряжения. Цепь подавления выбросов при включении, использующая изменение скважности импульсов, эффективно справляется с выбросами тока.

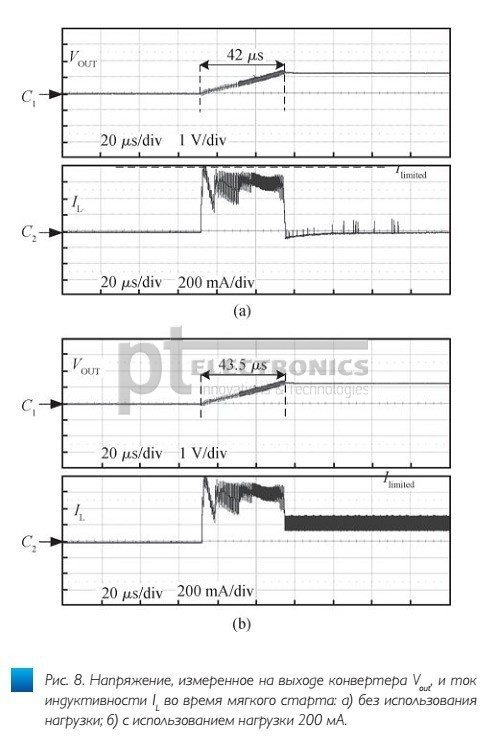

Рис. 8 иллюстрирует напряжение, измеренное на выходе конвертера, и ток индуктивности во время мягкого старта без использования нагрузки (8а), а также с использованием нагрузки (8б). Экспериментальные данные соответствуют результатам анализа, которые не вызывали всплеска напряжения и тока. Время мягкого старта составляет всего лишь 43,5 мкс.

Заключение

В статье описана встроенная цепь мягкого старта, состоящая из цепи подавления перерегулирования и цепи подавления выбросов тока. Цепь подавления перерегулирования генерирует плавно возрастающее напряжение, которое может эффективно подавлять превышения выходного напряжения. Цепь подавления выбросов при включении, использующая изменение скважности импульсов, эффективно справляется с выбросами тока. Результаты моделирования показывают, что предложенная схема высокоскоростного мягкого старта, встраиваемая в DC/DC-преобразователь, полностью соответствует теоретическим результатам. Тестовый чип был изготовлен с использованием 0,13-мкм CMOS-технологии, что позволяет сравнить практические результаты с теоретическим анализом. Результаты теста показывают, что данная технология позволяет достигнуть очень короткого времени старта, порядка 43,5 мкс. Более того, благодаря тому, что данная схема мягкого пуска выполнена с помощью CMOS-процесса, ее легко перенести на другие преобразователи.

отправка...

отправка...