Назад

Безлицензионный высокоскоростной АЦП LM15851

Автор статьи

(Опубликовано в журнале «Вестник Электроники» №1 2015)

Скачать статью в формате PDF (575 КБ)

Компания Texas Instruments является одним из ведущих производителей микросхем сверхвысокочастотных АЦП, а также других интегральных ВЧ-устройств для спектральной цифровой обработки, работающих в гигагерцовом диапазоне преобразования. Позиции фирмы были значительно усилены в данном секторе благодаря использованию технологий, разработанных ранее компанией National Semiconductor, которая стала подразделением TI после ее приобретения компанией TI в апреле 2011 года.

Сверхвысокочастотные АЦП широко используются в цифровых осциллографах, тестовых измерительных приборах, промышленных АЦП, автоматизированном тестовом оборудовании для микросхем и приборов, а также радарных системах и сканерах, в медицинском диагностическом оборудовании, в приемниках базовых станций мобильной связи (GSM/EDGE, CDMA2000, UMTS, LTE и WiMax), в широкодиапазонных цифровых приемниках и сканерах. Находят применение высокочастотные АЦП и для цифровой коррекции предыскажений ВЧ-сигналов. В данной статье рассматривается структура и принцип работы микросхемы LM15851, которая благодаря своим уникальным характеристикам может найти широкое применение в ряде секторов беспроводной связи и широковещательных систем связи.

Микросхема LM15851 является интегральным устройством для применения в широкодиапазонных цифровых приемных устройствах, содержащим целую систему аналоговой и цифровой обработки, модуль сверхширокополосного сэмплирования и цифровой фильтрации и подстройки частоты, а также современный интерфейс для последовательной передачи выходного цифрового потока данных. Устройство комбинирует системы для реализации AFE сверхскоростной с конфигурируемым цифровым блоком частотной настройки. Такая комбинация обеспечивает отличные характеристики для разработки гибких программно настраиваемых подсистем для цифровых тюнеров с широкой полосой для связных радиостанций для различных приложений.

Основные параметры микросхемы LM15851

-

Максимальная частота выборок: 4000 MSPS. - Минимальная частота выборок: 1000 MSPS.

- Размер цифрового слова с выхода DDC: 30 разрядов (комплексное число I/Q).

- Малый уровень шума и высокая линейность вплоть до частот 3 ГГц.

- Конфигурируемый режим DDC.

- Программируемый фактор децимации от 4 до 32.

- При 4000 MSPS и 4-кратном факторе децимации достижима полоса полезного сигнала 800 МГц.

- При 4000 MSPS и 32-кратном факторе децимации достижима полоса полезного сигнала 100 МГц.

- IMD3 (интермодуляционные искажения): –64 dBc (Fin=2140 МГц+–30 МГц при -13 dBFS).

- FPBW (–3 dB) полный диапазон входного сигнала, при котором гарантируется преобразование с уменьшением мощности сигнала на 3 дБ: 3,2 ГГц.

- Низкая величина джиттера выходного сигнала: менее 1,4 пс при 8000 МГц.

- Низкопрофильный интерфейс класса 1 JESD204B с малым числом выводов.

- Автоматический выбор и определение числа линий интерфейса JESD204B.

- Встроенный сигнал контроля уровня выходного сигнала с малой задержкой.

- Малое потребление: 2 Вт (при 4000 MSPS и факторе децимации 10).

- В неактивном режиме: менее 50 мВт .

- Напряжения питания: 1,9 В и 1,2 В.

- Корпус: низкопрофильный VQFN-68 с размером 10х10 мм.

- Рабочий температурный диапазон: –40…+85 °C

- Температура хранения: –65…+150 °С.

Области применения

- Беспроводные системы передачи данных.

- RF-сэмплинг для SDR (Software Defined Radio) приемников, например в автомагнитолах или музыкальных центрах.

- Приемники радиорелейных каналов телекоммуникационных сетей.

- Приемники Data Over Cable Service Interface Specification (DOCSIS) – для сетей кабельного телевидения.

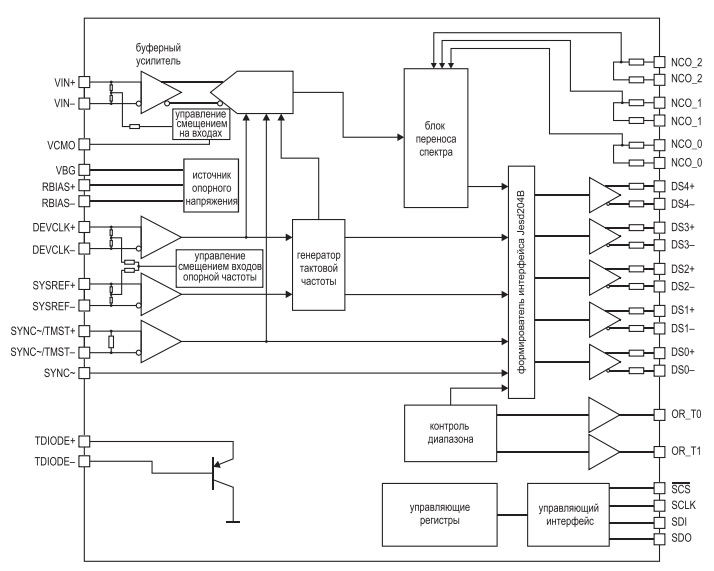

Основой LM15851 является ядро сверхскоростного модуля АЦП, имеющего разрядность 12 бит. Для обеспечения такой высокой скорости сэмплирования используется архитектура с конвейерным преобразованием, калибровкой и интерполяцией, что обеспечивает высокую скорость сэмплирования наряду с очень высокими динамическими характеристиками и относительно низким энергопотреблением. После блока АЦП используется конфигурируемый блок DDC (Digital Down Converter), который реализован на очень малой площади КМОП-кристалла. Блок DDC обеспечивает прореживание (децимацию) данных выходного потока данных АЦП. Установка различных коэффициентов прореживания позволяет управлять полосой приемника (ultra-wideband, wideband или more-narrow-band) в системах связи. Выходной цифровой поток данных с выхода DDC блока направляется далее в кодер стандартного интерфейса JESD204B для последовательной передачи данных к потребителю (DSP, ASIC, FPGA). Кодер обеспечивает форматирование данных, скремблирование и кодирование в коде 8b10 B для улучшения помехоустойчивости канала передачи. Кроме того, кодер позволяет оптимизировать число линий, необходимых для передачи суммарного последовательного цифрового потока.

Входной дифференциальный сигнал имеет емкостную развязку с источником сигнала. Диапазон входного сигнала – не более 2 В. Во входной цепи имеется схема балансировки дифференциальных сигналов, а также схема калибровки, что позволяет значительно улучшить качество преобразования. Входной импеданс дифференциального входа усилителя образован двумя 50-омными резисторами, подключенными к общей земляной цепи. В микросхеме используется встроенный источник опорного напряжения, который может корректироваться внешней настройкой.

Входной аналоговый сигнал защелкивается по переднему фронту сигнала CLK. Микросхема LM15851 работает только при наличии на ее входе сигнала синхронизации CLK.

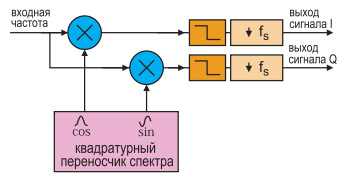

Рис. 2. Структура с аналоговой обработкой и выделение квадратурных составляющих полезного спектра I/Q

Цифровые радиоприемники часто содержат в составе блока DDC высокоскоростной АЦП. В зависимости от способа преобразования АЦП мог оцифровывать весь входной ВЧ-сигнала (несущая + сигнал модуляции) или оцифровывать сигнал только промежуточной частоты. В обоих случаях полезная информация содержится лишь в малом полезном частотном диапазоне. Для выделения полезного сигнала требуется устанавливать сложный фильтр. Использование DDC позволяет в цифровой форме производить фильтрацию полезного спектра из оцифрованного сигнала. Демодуляция и выделение данных производится в последующих блоках, входящих в состав FPGA или ASIC.

В приемнике с полностью аналоговой обработкой спектра применяются смесители и квадратурные синтезаторы частоты или же гетеродинные генераторы sin и cos. С помощью смесителей производилось понижение спектра полезного сигнала, фильтрация, а затем и демодуляция полезных составляющих спектра I/Q.

Как работает DDC?

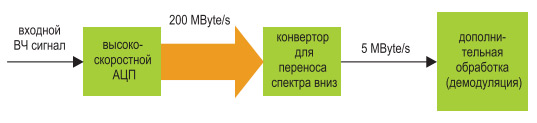

На рис. 3 показана структура тракта цифрового приемника с DDC.

После АЦП образуется цифровой поток с полосой 200 байт/с. Только малая часть полезного сигнала содержится в данном потоке. Блок DDC позволяет уменьшить полосу выходного потока за счет переноса спектра полезного сигнала.

Комментарий специалиста

Комментарий специалиста

Сергей Гавриленко, инженер по внедрению PT Electronics, sergey.gavrilenko@ptelectronics.ru

Данная микросхема приобретает огромную актуальность на российском рынке, так как она поставляется без оформления каких-либо лицензий. АЦП обладает достойными характеристиками: высокой частотой сэмплирования до 4 ГГц, широкой полосой входного сигнала, 12 битовой разрядностью. Также в LM15851 иcпользуется современный выходной интерфейс JESD204B, который позволяет в разы увеличить скорость передачи данных и при этом уменьшить занимаемое пространство на плате.

Рассмотрим, например, радиосигнал, лежащий в диапазоне 39–40 МГц. Полоса полезного сигнала лежит в полосе 1 МГц. Однако обычно оцифровка производится с частотой 100 Mсэмпл/с, что соответствует частотам 200 Мбайт/с. Применение DDC позволяет выделить полосу 39–40 MГц и сдвинуть частоту полезного сигнала вниз до 1 MГц и упростить дальнейшую обработку. При этом достаточно будет использовать скорость выборки сэмплов всего 2,5 MГц, а скорость цифрового потока понизится до 5 Mбайт/с.

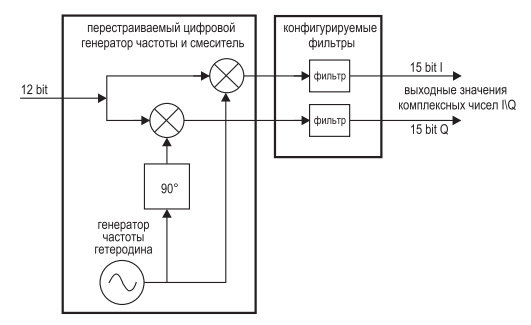

На вход блока DDC поступает сэмплированный 12-разрядный поток от АЦП. В первой ступени DDC производится выделение двух квадратурных потоков I/Q за счет использования смесителей частот, сдвинутых по фазе на 90°. Во второй секции DDC производится фильтрация сигналов в каналах I и Q за счет конфигурируемых прореживаний отсчетов данных. На выходе фильтров получаем комплексное 30-разрядное число (15 бит I и 15 бит Q).

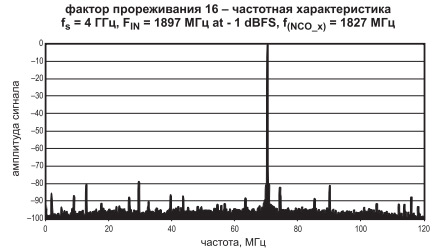

На рис. 5 показана спектральная характеристика выходного сигнала при заданных параметрах входной частоты сэмплирования, заданном факторе децимации в блоке DDC.

Интерфейс JESD204B

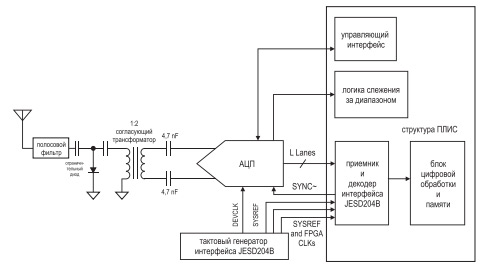

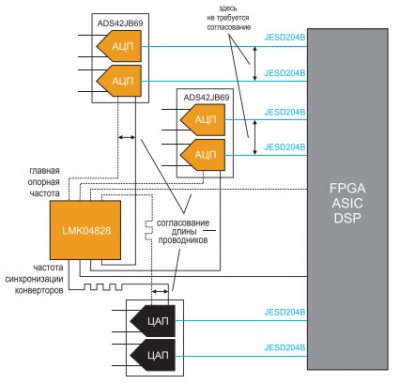

Рис. 6. Применение интерфейса по стандарту JESD204B позволяет значительно упростить взаимную синхронизацию потоков данных от различных конвертеров, работающих в единой сетке системной синхронизации

Увеличение скоростей преобразования аналог-цифра и наоборот потребовало и увеличения скоростей передачи данных до устройства их обработки. До скоростей преобразования 10 Мbps/c использовались обычные параллельные шины с уровнями сигналов LVCMOS. Для передачи 16-разрядного параллельного кода требовалось 17 проводников на печатной плате) 16 данные + сигнал тактирования). При возрастании скоростей преобразования АЦП и ЦАП до уровня 1 Gbps для передачи скоростных потоков данных стали использоваться дифференциальные сигналы и последовательные протоколы передачи. Это позволило не только увеличить скорости передачи, но и оптимизировать пространство, занимаемое шиной данных конвертеров на печатной плате. 1-й вариант стандарта JESD204A был ориентирован на организацию высокоскоростной передачи данных между конвертерами (ЦАП или АЦП) и устройствами обработки (DSP, ASIC, FPGA). В первой версии стандарта для передачи скоростного потока можно было использовать от 1 до 2 дифференциальных пар (lane), которые были способны обеспечивать передачу сигналов до 3,125 Gbps. Уровни выходных дифференциальных сигналов – CML. В сигналах использовалась встроенная битовая синхронизация. В зависимости от режима могли использоваться или одна или две, что давало определенную свободу выбора при трассировке шины. Для улучшения надежности передачи за счет высокой устойчивости синхронизации данных в потоке стала использоваться скремблирование и избыточнее оверхед-кодирование 8b10b. Это мероприятие позволило исключать из последовательных потоков длинные последовательности нулей или единиц и улучшить выделение сигнала битовой синхронизации. Следующая версия стандарта, JESD204B, появилась в 2011 году и стала закономерным развитием предыдущей версии. Основным отличием стала возможность использовать большее число линий дифференциальных сигналов для повышения скоростей преобразования от 3,25 Gbps до 6,25 и 12,5 Gbps. Второе нововведение касалось возможности введения глобальной синхронизации нескольких потоков JESD204 от разных скоростных конвертеров за счет введения мастера опорной частоты.

В микросхеме LM15851 в зависимости от полосы полезного сигнала для передачи данных могут использоваться от одной дифференциальной CML-пары проводов до пяти.

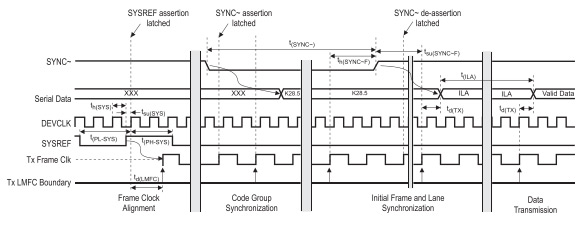

На рис. 7 показана временная диаграмма синхронизации сигналов интерфейса JESD204B для работы с несколькими источниками.

Управляющий интерфейс SPI

Для загрузки управляющих параметров в конфигурационные регистры микросхемы LM15851 используются сигналы стандартного интерфейса SPI. Ниже, на рис. 8, показаны диаграммы сигналов интерфейса SPI.

Корпус микросхемы и режимы охлаждения

Микросхема LM15851 размещена в компактном корпусе размером всего 10×10 мм. Выделяемая мощность (около 2 Вт) достаточно большая для данного компактного корпуса, поэтому для надежного функционирования требуется обеспечить надежный теплоотвод. В документации на микросхему приведены рекомендации по организации необходимого теплоотвода. Можно обойтись и без применения внешнего радиатора, если использовать в качестве теплоотвода участок фольги нижнего слоя печатной платы площадью от 1 до 2 см2.

Типичная схема применения микросхемы LM15851

На рис. 10 показана типовая схема включения микросхемы в цепи цифрового радиоприемного тракта.

Для обеспечения правильного функционирования микросхемы и достижения максимальных параметров, указанных в спецификации, требуется выполнение определенных требований по размещению сигналов, установке блокирующих конденсаторов для фильтрации по питанию. Пример оптимальной топологии при размещении микросхемы LM15851, а также трассировка сигналов по слоям печатной платы приведены в документации на микросхему.

Литература

- LM15851 Ultra-Wideband RF Sampling Subsystem. Texas Instruments. September 2014.

- The Theory of Digital Down Conversion. Hunt Engineering Rev 1.2 T.Hollis/R.Weir 26-06-2003

отправка...

отправка...